Label / Classification: This article refers to the address: http://

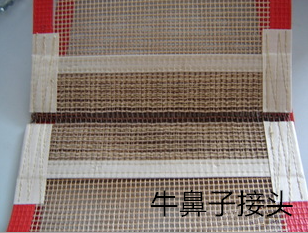

Bull nose is a common connecting way of Conveyor Belt, which is named for its shape.

The joint mesh is made of Kevlar coated with Teflon dispersion, whose technical is similar to PTFE open Mesh Conveyor Belt.

Compared to PTFE fabric conveyor belt, bull nose is much more suitable for open mesh conveyor belt, and easy to install and to repairing. In addition, the price is more competitive than alligator joint. Besides, the conveyor belt with bull nose can apply in micro wave situation.

PTFE Conveyor Belts With Bullnose Industrial Conveyor Belts,Conveyor Belt With Bullnose,Mesh Conveyor Belt With Bullnose,PTFE Conveyor Belts With Bullnose TAIZHOU YAXING PLASTIC INDUSTRY CO., LTD , https://www.yaxingptfe.com Automotive taillight VHDL design

1. System design requirements 6 LED lights are used to simulate 6 car taillights (3 on each side), and 4 switches are used as vehicle control signals: left turn, right turn, fault and brake.

When the car is driving at a constant speed, the 6 taillights of the car are completely extinguished; when turning right, the 3 taillights on the right side of the car are sequentially turned off from left to right; when turning left, the 3 taillights on the left side of the car are sequentially turned off from right to left; One taillight flashes together; when braking, 6 taillights are fully illuminated

2. System design scheme According to the system design requirements, the top-down design method is adopted. The top-level design adopts the schematic design. It consists of three parts: the main control module, the left-side light control module and the right-side light control module.

3 Reference VHDL source program (1) Main control module Description: This program is the system main control module. When turning left, the lft signal is valid; when turning right, the rit signal is valid; when the left and right signals are valid, lr is valid.

Library ieee;

Use ieee.std_logic_1164.all;

Entity kz is

Port(left,right:in std_logic;

Lft, rit, lr: out std_logic);

End kz;

Architecture kz_arc of kz is

Begin

Process(left,right)

Variable a:std_logic_vector(1 downto 0);

Begin

a:=left&right;

Case a is

When"00"=>lft<='0';

Rit<='0';

Lr<='0';

When"10"=>lft<='1';

Rit<='0';

Lr<='0';

When"01"=>rit<='1';

Lft<='0';

Lr<='0';

When others=>rit<='1';

Lft<='1';

Lr<='1';

End case;

End process;

End kz_arc;

(2) Left light control module description: The function of this module is to control the three lights on the left when turning left. When the left and right signals are valid, the output is all "1".

Library ieee;

Use ieee.std_logic_1164.all;

Entity lfta is

Port(en,clk,lr:in std_logic;

L2, l1, l0: out std_logic);

End lfta;

Architecture lft_arc of lfta is

Begin

Process(clk,en,lr)

Variable tmp:std_logic_vector(2 downto 0);

Begin

If lr='1' then

Tmp:="111";

Elsif en='0' then

Tmp:="000";

Elsif clk'event and clk='1' then

If tmp="000" then

Tmp:="001";

Else

Tmp:=tmp(1 downto 0)&'0';

End if;

End if;

L2<=tmp(2);

L1<=tmp(1);

L0<=tmp(0);

End process;

End lft_arc;

(2) Right light control module description: The function of this module is to control the 3 lights on the right, similar to the above module.

Library ieee;

Use ieee.std_logic_1164.all;

Entity rita is

Port(en,clk,lr:in std_logic;

R2,r1,r0:out std_logic);

End rita;

Architecture rit_arc of rita is

Begin

Process(clk,en,lr)

Variable tmp:std_logic_vector(2 downto 0);

Begin

If lr='1' then

Tmp:="111";

Elsif en='0' then

Tmp:="000";

Elsif clk'event and clk='1' then

If tmp="000" then

Tmp:="100";

Else

Tmp:='0'&tmp(2 downto 1);

End if;

End if;

R2<=tmp(2);

R1<=tmp(1);

R0<=tmp(0);

End process;

End rit_arc;