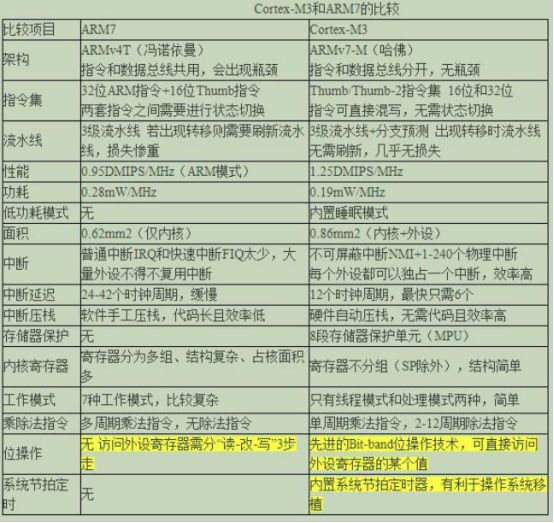

Why does ARM have two startup methods? What is the difference between ARM7 and ARM-Cortex? What's the matter with fast interruption and interruption? Why are there two booting methods for ARM's two booting methods (NAND FLASH. NOR FLASH)? This is mainly determined by the different characteristics of the two FLASH. NAND FLASH has a large capacity, and the cost of storing unit bit data is much lower. However, NAND FLASH must be read and written according to a specific timing. Therefore, the CPU cannot directly address the data in NAND FLASH. The CPU reads the data in NAND FLASH. Writing is performed through a special nand flash controller, so NAND FLASH is more suitable for storing data. NOR FLASH has small capacity and fast speed. When reading and writing NOR FLASH, input the address, and then give the read and write signal to get data from the data bus, but the price is higher than NAND FLASH, so it is suitable for program memory. In summary, NOR FLASH can be directly connected to the arm bus, but DAND FLASH needs to be connected to S3S2440 through a NAND FLASH controller. The difference between ARM7 and ARM-Cortex ARM7: ARMv4 architecture, ARM9: ARMv5 architecture, ARM11: ARMv6 architecture, ARM-Cortex series: ARMv7 architecture. ARM7 has no MMU (memory management unit), it can only be called MCU (microcontroller), and cannot run modern multi-user and multi-process operating systems such as Linux, WinCE, etc., because running these systems requires MMU to assign each user process The process has its own independent address space. Streamlined real-time RTOSs such as ucOS and ucLinux do not require MMU, and of course they can run on ARM7. ARM9 and ARM11 are embedded CPUs (processors) with MMU, which can run multi-user and multi-process operating systems such as Linux. The application scenarios are also different from ARM7. When it came to the ARMv7 architecture, it began to be named after Cortex and divided into three series: Cortex-A, Cortex-R, and Cortex-M. The three series have a clear division of labor: the "A" series are for cutting-edge virtual memory-based operating systems and user applications; the "R" series are for real-time systems; and the "M" series are for microcontrollers. Simply put, the Cortex-A series are CPUs used in the mobile field, and the Cortex-R and Cortex-M series are MCUs used in the real-time control field. So it looks like ARM7 is very similar to Cortex-M, because they are both MCUs, but they are MCUs of different generations and different architectures (Cortex-M is three generations higher than ARM7!), so there is a big gap in performance. In addition, the Cortex-M series is also subdivided into M0, M3, M4 and ultra-low power M0+. Users choose chips based on factors such as cost, performance, and power consumption. I must know the difference between ARM7 and Cortex-M by now, but the editor took some time to organize it here, which can help later beginners understand these basic conceptual issues. ARM's FIQ (Fast Interrupt) IRQ (Interrupt) IRQ, FIQ definition: This is an ordinary interrupt, when our program defines the interrupt, and an IRQ interrupt is generated when the program is running, then the chip is running like this at this time ------ use the interrupt processor The IRQ request line comes to high-speed ARM, and ARM knows that an IRQ interrupt is coming, and then ARM switches to IRQ mode to run. Similarly, if the interrupt is set to FIQ, then when the interrupt is generated, the interrupt processor tells ARM through the FIQ request line, ARM knows that a FIQ interrupt is coming, and then switches to FIQ mode to run. So the question is, why are there these two interrupts, or why are they divided into these two interrupts? The reason is very simple, the speed is different, FIQ is the fast interruption speed, then the problem comes again, why is the FIQ fast??? reason: 1: ARM's FIQ mode provides more banked registers, r8 to r14 and SPSR, but IRQ mode does not have that many, R8, R9, R10, R11, R12 corresponding banked registers are not available, which means In the IRQ mode of ARM, the interrupt handler itself must save the registers R8 to R12, and then the program must restore these registers when exiting the interrupt handler. In the FIQ mode, because these registers have banked registers, when the mode is switched The CPU automatically saves these values ​​to the banked register and automatically restores it when exiting FIQ mode, so this process is faster than IRQ. Don’t underestimate these registers. When ARM is compiling, if your FIQ interrupt handler is enough to use these independent It does not push general-purpose registers on the stack, which saves some time. 2: FIQ has a higher priority than IRQ. If FIQ and IRQ are generated at the same time, FIQ will be processed first. 3: In the Symbian system, when the CPU is in FIQ mode to process FIQ interrupts, prefetch instruction exceptions, undefined instruction exceptions, software interrupts are all disabled, and all interrupts are masked. Therefore, FIQ will be executed quickly and will not be interrupted by other exceptions or interrupts, so it is faster than IRQ. The IRQ is different. When the ARM processes the IRQ mode to process the IRQ interrupt, if a FIQ interrupt request comes, the IRQ interrupt handler being executed will be preempted, and the ARM switches to the FIQ mode to execute the FIQ, so FIQ is faster than IRQ too much. 4: In addition, the entry address of FIQ is 0x1c, and the entry address of IRQ is 0x18. Those who have written the complete assembly system understand the difference. 18 can only put one instruction. In order not to conflict with FIQ at 1C, this place can only jump, and FIQ is different. After 1C, there is no interrupt vector table. In this way, the FIQ interrupt handler can be placed directly at 1C. Due to the limit of the jump range, at least one jump instruction is missing. SHAOXING COLORBEE PLASTIC CO.,LTD , https://www.fantaicolorbee.com