How to automatically cover 99.99% of the situation Vacuum Cleaner Brushless Motor-BLDC Vacuum Cleaner Brushless Motor-Bldc,Brushless Motor Cordless Vacuum Cleaner,Brushless Motor Vacuum Cleaner,Vacuum Cleaner For With Brushless Motor Zhoushan Chenguang Electric Appliance Co., Ltd. , https://www.vacuum-cleaner-motors.com

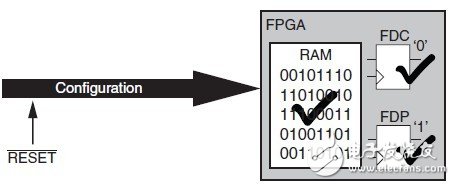

As Xilinx's FPGA chips are increasingly embedded in processor cores, such as MicroBlaze soft cores, ARM and PowerPC hard cores, this feature allows all program and data space to be before the processor core executes the first instruction. Pre-defined, the original operation of simply resetting the trigger by burning expensive programmable resources becomes meaningless. The simulation tools used in the development process should also have the ability to simulate this operation (ie, what we call "power-on reset"), so that unnecessary reset operations can be avoided in subsequent designs.

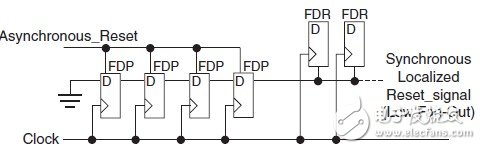

The most important thing in the design guidelines for the remaining 0.01% is to use certain criteria to handle the reset operations in the design, and these guidelines should be fully considered during the design review phase. A local high performance reset network can be used to control flip-flops that only require partial reset. Figure 7 shows a schematic of such a partial reset. The advantage of this circuit is that it provides a reset effect that is consistent with the effect of an external global reset signal.

The number of flip-flops in the chain determines the minimum width of the reset pulse required to locally reset the network. The net result is that the last flip-flop in the chain transitions from high to low, while the release of the local reset signal is synchronized with the clock cycle. The reset flip-flop can use synchronous set (FDS) or synchronous reset (FDR), which constitutes a complete synchronous design, and the subsequent timing specification and analysis will be much easier.

Figure 7 partial reset diagram

All triggers in the chain are preset to 1 during device configuration or asynchronous reset. Almost at the same time, the last trigger in the chain drives the local reset network and sends a valid reset signal to it. As the global reset/set signal or the asynchronous reset signal is released, the entire shift register chain begins to be filled with zeros every clock cycle.